���D��2-10�M���g�a��74LS42�Ȳ��Y��,���_�D����ֵ��

(2023/5/6 11:00:00)

2-10�M���g�a��74LS42�Ȳ��Y��,���_�D����ֵ��

2-10�M���g�a��74LS42�Ȳ��Y��,���_�D����ֵ��

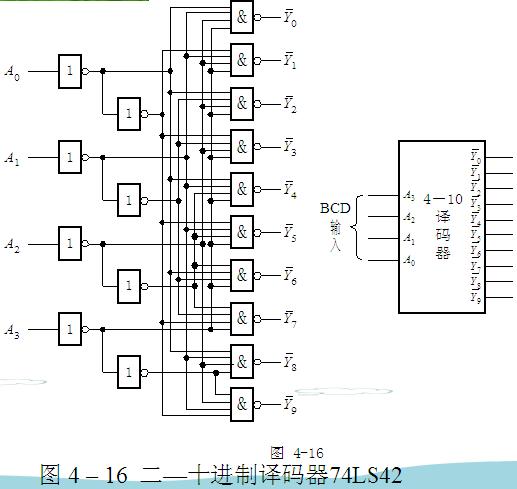

��ݔ���8421BCD���a���g��10��������ݔ����̖���Á���ʾ0��9 ��10�����֣���߉�·�Q�����ʮ�M���g�a�����D4.15�o���˶���ʮ�M���g�a��74LS42��߉�D��

�D4.15 ����ʮ�M���g�a��74LS42߉�D

����߉�D���Ԍ������_ʽ����ʽ4.5��ʾ��

��4.9 74LS42���ܱ�

2-10�M���g�a��74LS42�Ȳ��Y��,���_�D����ֵ��

��ݔ���8421BCD���a���g��10��������ݔ����̖���Á���ʾ0��9 ��10�����֣���߉�·�Q�����ʮ�M���g�a�����D4.15�o���˶���ʮ�M���g�a��74LS42��߉�D��

�D4.15 ����ʮ�M���g�a��74LS42߉�D

����߉�D���Ԍ������_ʽ����ʽ4.5��ʾ��

��4.9 74LS42���ܱ�

����ʽ4.5�����г���ֵ�������4.9��ʾ���ɱ�4.9���Կ�����ԓ�·ݔ�����8421BCD�a��ʮ��ݔ����Y0 ~Y9���g�aݔ���r��“0”���]���g�aݔ���r��“1”����“���ƽ”����Чݔ����̖�����Ԯ�ݔ���1010��1111 6���oЧ��̖�r���g�a��ݔ��ȫ“1”�������oЧ��̖�ܽ^�g�a��

�g�[��(2610)| �uՓ(

0

)

- ��һƪ�� �\��Ŵ����ij��ü��gָ��

![IC�]ُ�W���Ԫ��Ʒ�|����](/static/img/950.jpg)