λ��λ�惦�����Ĵ���CD4094�����Y��

CD4094�ǎ�ݔ���i������B���ƵĴ���/���������D�Q��������ʹ�ú��Ρ����ĵ͡����������Ϳ����`��ȃ��c��

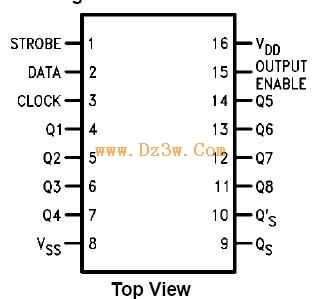

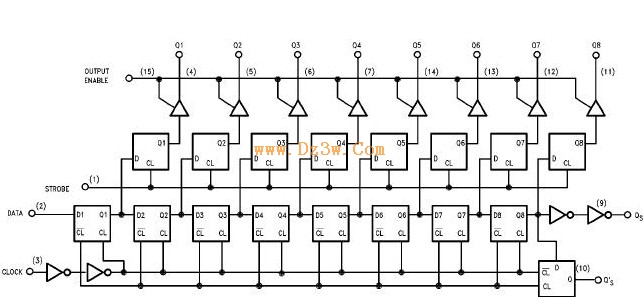

CD4094�����_�D�����_����

����(1)�_���i��ˣ�

(2)�_�鴮�Д���ݔ��ˣ�

(3)�_�鴮�Еr状ˡ�(1)�_����ƽ�r��8λ����ݔ����Q1��Q8�ڕr犵��������S����ݔ���׃����(1)�_����ƽ�r��ݔ���i���������i��˿ɷ�����M��Ƭ�x�ͼ�ݔ�����ơ�

(15)�_�鲢��ݔ����B���ƶˣ�(15)�_����ƽ�r������ݔ����̎�ڸ����B������CD4094���@ʾݔ���r����ʹ�@ʾ���a�W�q��(

9)�_QS��(10)�_Q′S�Ǵ��Д���ݔ���ˣ����ڼ���QS���ڵ�9�����Еr犵��������_ʼݔ����Q′S���ڵ�9�����Еr犵��½����_ʼݔ����

��CD4094�Դ��5V�r��ݔ���������3��2MA���������1 MA�����Еr��l�ʿ��_2��5MHZ��

CD4094���_�D

CD4094��ֵ����

Clock

| Output Enable

| Strobe

| Data

| Parallel Outputs ����ݔ��

| Serial Outputs ����ݔ��

| ||

Q1

| QN

| QS (Note 1)

| Q S

| ||||

↑

| 0

| X

| X

| ���B

| ���B

| Q7

| ��׃

|

↓

| 0

| X

| X

| ���B

| ���B

| ��׃

| Q7

|

↑

| 1

| 0

| X

| ��׃

| ��׃

| Q7

| ��׃

|

↑

| 1

| 1

| 0

| 0

| QN-1

| Q7

| ��׃

|

↑

| 1

| 1

| 1

| 1

| QN-1

| Q7

| ��׃

|

↓

| 1

| 1

| 1

| ��׃

| ��׃

| ��׃

| Q7

|

CD4094�Ȳ��·����D

Absolute Maximum Ratings �^������~��ֵ��

Supply Voltage�Դ늉�(VDD)

| -0.5 to +18 VDC

|

Input Voltageݔ��늉� (VIN)

| -0.5 to VDD +0.5 VDC

|

Storage Temperature Range����ضȷ��� (TS)

| -65�� to +150��

|

Power Dissipation���� (PD)

| |

Dual-In-Line ��ͨ�p�з��b

| 700 mW

|

Small Outline С���η��b

| 500 mW

|

Lead Temperature ���Ӝض�(TL)

| |

Soldering, 10 seconds)������10�룩

| 260��

|

Recommended Operating Conditions ���h�����l����

DC Supply Voltage ֱ�����늉� (VDD)

| +3.0 to +15 VDC

|

Input Voltageݔ��늉� (VIN)

| 0 to VDD VDC

|

Operating Temperature Range�����ضȷ��� (TA)

| -40�� to +85��

|

DC Electrical Characteristics ֱ��늚����ԣ�

Symbol��̖

| Parameter����

| Conditions �l��

| -40°C

| +25°C

| +85°C

| Units ��λ

| |||||

��С

| ���

| ��С

| ����

| ���

| ��С

| ���

| |||||

IDD

| Quiescent Device Current�o�B���

| VDD = 5.0V

|

| 20

|

|

| 20

|

| 150

| μA

| |

VDD = 10V

|

| 40

|

|

| 40

|

| 300

| ||||

VDD = 15V

|

| 80

|

|

| 80

|

| 600

| ||||

VOL

| LOW Level Output Voltage ݔ�����ƽ늉�

| VDD=5.0V

| |IO|≤1.μA

|

| 0.05

|

| 0

| 0.05

|

| 0.05

| V

|

VDD=10V

|

| 0.05

|

| 0

| 0.05

|

| 0.05

| ||||

VDD=15V

|

| 0.05

|

| 0

| 0.05

|

| 0.05

| ||||

VOH

| HIGH Level Output Voltage ݔ�����ƽ늉�

| VDD=5.0V

| |IO|≤1μA

| 4.95

|

| 4.95

| 5.0

|

| 4.95

|

| V

|

VDD=10V

| 9.95

|

| 9.95

| 10.0

|

| 9.95

|

| ||||

VDD=15V

| 14.95

|

| 14.95

| 15.0

|

| 14.95

|

| ||||

VIL

| LOW Level Input Voltage ݔ����ƽ늉�

| VDD = 5.0V, VO = 0.5V or 4.5V

|

| 1.5

|

|

| 1.5

|

| 1.5

| V

| |

VDD = 10V, VO = 1.0V or 9.0V

|

| 3.0

|

|

| 3.0

|

| 3.0

| ||||

VDD = 15V, VO = 1.5V or 13.5V

|

| 4.0

|

|

| 4.0

|

| 4.0

| ||||

VIH

| HIGH Level Input Voltage ݔ����ƽ늉�

| VDD = 5.0V, VO = 0.5V or 4.5V

| 3.5

|

| 3.5

|

|

| 3.5

|

| V

| |

VDD = 10V, VO = 1.0V or 9.0V

| 7.0

|

| 7.0

|

|

| 7.0

|

| ||||

VDD = 15V, VO = 1.5V or 13.5V

| 11.0

|

| 11.0

|

|

| 11.0

|

| ||||

IOL

| LOW Level Output Current ݔ�����ƽ��� (Note 4)

| VDD=5.0V,VO=0.4V

| 0.52

|

| 0.44

| 0.88

|

| 0.36

|

| mA

| |

VDD=10V,VO=0.5V

| 1.3

|

| 1.1

| 2.25

|

| 0.9

|

| ||||

VDD=15V,VO=1.5V

| 3.6

|

| 3.0

| 8.8

|

| 2.4

|

| ||||

IOH

| HIGH Level Output Current ݔ�����ƽ��� (Note 4)

| VDD=5.0V,VO =4.6V

| -0.52

|

| -0.44

| 0.88

|

| -0.36

|

| mA

| |

VDD =10V,VO= 9.5V

| -1.3

|

| -1.1

| 2.25

|

| -0.9

|

| ||||

VDD=15V,VO =13.5V

| -3.6

|

| -3.0

| 8.8

|

| -2.4

|

| ||||

IIN

| Input Current ݔ�����

| VDD =15V,VIN =0V

|

| -0.3

|

|

| -0.3

|

| -1.0

| μA

| |

VDD=15V,VIN =15V

|

| 0.3

|

|

| 0.3

|

| 1.0

| ||||

IOZ

| 3-STATE Output Leakage Current 3�Bݔ��©���

| VDD=15V,VIN=0V or 15V

|

| 1

|

|

| 1

|

| 10

| μA

| |

AC Electrical Characteristics ����늚����ԣ�

Symbol ��̖

| Parameter ����

| Conditions �l��

| ��С

| ����

| ���

| Units ��λ

|

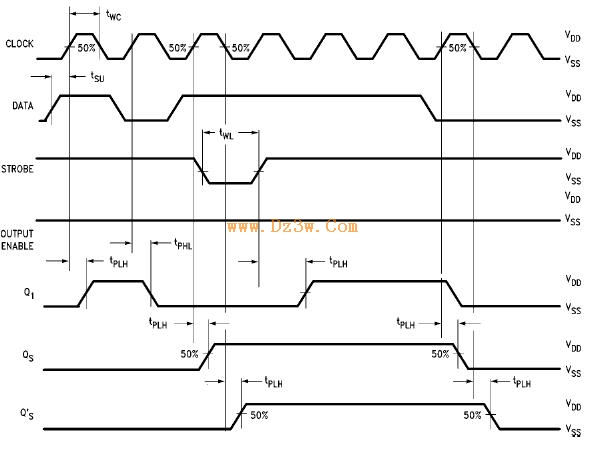

tPHL, tPLH

| Propagation Delay Clock to QS

| VDD = 5.0V

|

| 300

| 600

| ns

|

VDD = 10V

|

| 125

| 250

| |||

VDD = 15V

|

| 95

| 190

| |||

tPHL, tPLH

| Propagation Delay Clock to Q¢ S

| VDD = 5.0V

|

| 230

| 460

| ns

|

VDD = 10V

|

| 110

| 220

| |||

VDD = 15V

|

| 75

| 150

| ns

| ||

tPHL, tPLH

| Propagation Delay Clock to Parallel Out

| VDD = 5.0V

|

| 420

| 840

| ns

|

VDD = 10V

|

| 195

| 390

| |||

VDD = 15V

|

| 135

| 270

| |||

tPHL, tPLH

| Propagation Delay Strobe to Parallel Out

| VDD = 5.0V

|

| 290

| 580

| ns

|

VDD = 10V

|

| 145

| 290

| |||

VDD = 15V

|

| 100

| 200

| |||

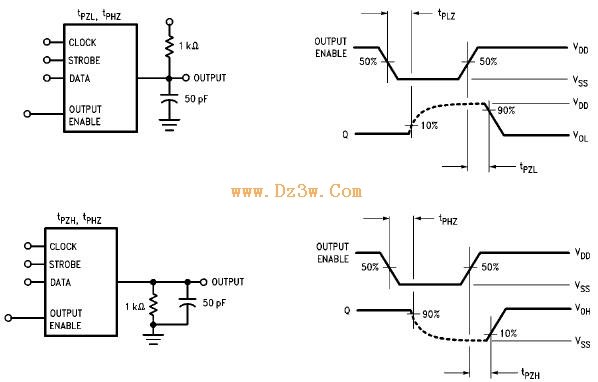

tPHZ

| Propagation Delay HIGH Level to HIGH Impedance

| VDD = 5.0V

|

| 140

| 280

| ns

|

VDD = 10V

|

| 75

| 150

| |||

VDD = 15V

|

| 55

| 110

| |||

tPLZ

| Propagation Delay LOW Level to HIGH Impedance

| VDD = 5.0V

|

| 140

| 280

| ns

|

VDD = 10V

|

| 75

| 150

| |||

VDD = 15V

|

| 55

| 110

| |||

tPZH

| Propagation Delay HIGH Impedance to HIGH Level

| VDD = 5.0V

|

| 140

| 280

| ns

|

VDD = 10V

|

| 75

| 150

| |||

VDD = 15V

|

| 55

| 110

| |||

tPZL

| Propagation Delay HIGH Impedance to LOW Level

| VDD = 5.0V

|

| 140

| 280

| ns

|

VDD = 10V

|

| 75

| 150

| |||

VDD = 15V

|

| 55

| 110

| |||

tTHL, tTLH

| Transition Time�^�ɕr�g

| VDD = 5.0V

|

| 100

| 200

| ns

|

VDD = 10V

|

| 50

| 100

| |||

VDD = 15V

|

| 40

| 80

| |||

tSU

| Set-Up Time Data to Clock �����r�g�����r�

| VDD = 5.0V

| 80

| 40

|

| ns

|

VDD = 10V

| 40

| 20

|

| |||

VDD = 15V

| 20

| 10

|

| |||

tr, tf

| Maximum Clock Rise and Fall Time���r��������½��r�g

| VDD = 5.0V

| 1

|

|

| ms

|

VDD = 10V

| 1

|

|

| |||

VDD = 15V

| 1

|

|

| |||

tPC

| Minimum Clock Pulse Width���r��}�_����

| VDD = 5.0V

| 200

| 100

|

| ns

|

VDD = 10V

| 100

| 50

|

| |||

VDD = 15V

| 83

| 40

|

| |||

tPS

| Minimum Strobe Pulse Width

| VDD = 5.0V

| 200

| 100

|

| ns ��

|

VDD = 10V

| 80

| 40

|

| |||

VDD = 15V

| 70

| 35

|

| |||

fmax

| Maximum Clock Frequency ���r��l��

| VDD = 5.0V

| 1.5

| 3.0

|

| MHz

|

VDD = 10V

| 3.0

| 6.0

|

| |||

VDD = 15V

| 4.0

| 8.0

|

| |||

CIN

| Input Capacitance ݔ�����

| Any Input

|

| 5.0

| 7.5

| pF

|

�yԇ�·��3�B�r��D

�r��D

- ��һƪ�� ���D��CD4518/CD4520�����Y��

![IC�]ُ�W���Ԫ��Ʒ�|����](/static/img/950.jpg)